3nm 製程工藝將於今年進行試產,沒有意外的話, 2022 年量產沒有問題。在此基礎上,業界對 2nm 工藝的進展投入了更多的關注,特別是台積電於 2020 下半年宣布 2nm 製程獲得重大突破之後,人們對其更加期待了。

與此同時,就在前不久,有 19 個歐盟成員國簽署了一項聯合聲明,為 “ 加強歐洲開發下一代處理器和半導體的能力 ” 進行合作。其中包括逐漸向 2nm 製程節點發展的領先製造技術。此外,日本正在與台積電一起建立先進的 IC 封裝和測試工廠。台灣半導體研究中心(TSRI)開始與日本產業技術總合研究所(AIST)合作,開發新型晶體管結構。日本媒體指出,這有助於製造 2nm 及更先進製程晶片,他們計劃將合作成果應用在 2024 年後的新一代先進半導體當中。而 2024 年正是台積電 2nm 製程的量產年。

目前,距離 2nm 試產還有一段時間,各方面都在積極籌備當中,圍繞著晶圓廠台積電,各大半導體設備供應商、材料工藝服務商、 EDA 工具廠商,以及主要客戶,都開始將越來越多的精力向 2nm 轉移。

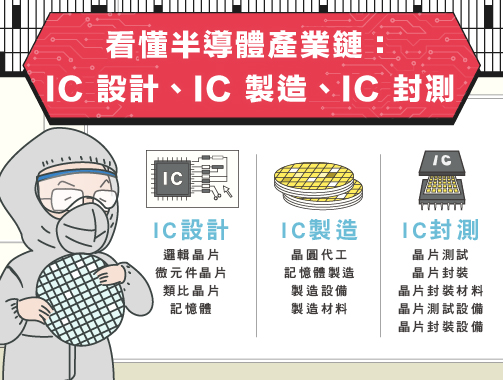

晶圓廠

目前來看,在 3nm 和 2nm 製程方面,台積電相對於三星的領先優勢很明顯,特別是 2nm ,還看不到來自於三星的權威資訊。2019 年,台積電率先開始了 2nm 製程技術的研發工作。相應的技術開發的中心和晶片生產工廠主要設在台灣的新竹,同時還規劃了 4 個超大型晶圓廠,主要用於 2nm 及更先進製程的研發和生產。

台積電 2019 年成立了 2nm 專案研發團隊,尋找可行路徑進行開發。在考量成本、設備相容、技術成熟及效能表現等多項條件之後,決定採用以環繞閘極(Gate-all-around, GAA )製程為基礎的 MBCFET 架構,解決 FinFET 因製程微縮產生電流控制漏電的物理極限問題。 MBCFET 和 FinFET 有相同的理念,不同之處在於 GAA 的柵極對溝道的四面包裹,源極和漏極不再和基底接觸。

根據設計的不同, GAA 也有不同的形態,目前比較主流的四個技術是奈米線、板片狀結構多路橋接鰭片、六角形截面奈米線、奈米環。與台積電一樣,三星對外介紹的 GAA 技術也是 Multi-Bridge Channel FET ( MBCFET ),即板片狀結構多路橋接鰭片。不過,三星在 3nm 節點處就使用了 GAA ,而台積電 3nm 使用的依然是 FinFET 工藝。

按照台積電給出的 2nm 工藝指標,Metal Track (金屬單元高度)和 3nm 一樣維持在 5x ,同時 Gate Pitch (晶體管柵極間距)縮小到 30nm ,Metal Pitch (金屬間距)縮小到 20nm ,相比於 3nm 都小了 23% 。

按照規劃,台積電有望在 2023 年中期進入 2nm 工藝試生產階段,並於一年後開始批量生產。 2020 年 9 月,據台灣媒體報導,台積電 2nm 工藝取得重大突破,研發進度超前,業界看好其 2023 年下半年風險試產良率就可以達到 90% 。

目前,除了晶圓廠建設、台積電 2nm 人才安排和培育方面的工作也正在有條不紊地進行著,據報導,該公司在過去幾個月提拔了 4 名員工。這些措施是為了讓這些員工有更多的精力投入到 2nm 製造工藝的研究和開發當中。據悉,Geoffrey Yeap 現在是 2nm 製程平台研發部的高級總監。這個位置在此之前是不存在的。當該公司開始專注於 2nm 製程時,創造這個位置是很重要的。台積電對管理人員的學術要求很高。兩位新提拔的副總經理都有博士學位。

設備

對於晶片製造來說,需要的設備很多,但就 2nm 這樣高精尖的工藝來講, EUV 光刻機無疑是最為關鍵的。有統計顯示,台積電 2021 年底將安裝超 50 台 EUV 光刻機。

對於台積電先進製程所需的 EUV 設備,有日本專家做過推理和分析:在 EUV 層數方面, 7nm +為 5 層, 5nm 為 15 層, 3nm 為 32 層, 2nm 將達 45 層。因此,到 2022 年,當 3nm 大規模生產、 2nm 準備試產,需要的新 EUV 光刻機數量預計為 57 台。 2023 年,當 3nm 生產規模擴大、 2nm 開始風險生產時,所需新 EUV 光刻機數達到 58 台。到 2024 年,啟動 2nm 的大規模生產, 2025 年生產規模擴大,到時所需新 EUV 光刻機數預計為 62 台。

儘管 EUV 也將被用於 DRAM (尤其是 1a 技術節點及以下),但採用先進製程的邏輯晶片仍是主要需求方。High-NA EUV 光刻系統將始於 2nm 製程節點,其量產時間預估將是 2025-2026 年。據悉, ASML 將在 2022 年完成第 1 台High-NA EUV 光刻機系統的驗證,並計劃在 2023 年交付給客戶,主要就是台積電。

對於 EUV 技術,台積電表示,要減少光刻機的掩膜缺陷及製程堆疊誤差,並降低整體成本。今年在 2nm 及更先進製程上,將著重於改善極紫外光技術的品質與成本。之前據消息指出,台積電正在籌集更多的資金,為的是向 ASML 購買更多更先進製程的 EUV 光刻機,而這些都是為了新製程做準備。對於 2nm 和更先進製程工藝來說, EUV 光刻機的重要性越來越高,但是 EUV 設備的產量依然是一大難題,而且其能耗也很高。

在不久前舉辦的線上活動中,歐洲微電子研究中心 IMEC 執行長兼總裁 LucVandenhove 表示,在與 ASML 公司的合作下,更加先進的光刻機已經取得了進展。

LucVandenhove表示, IMEC 的目標是將下一代高解析度 EUV 光刻技術高 NAEUV 光刻技術商業化。由於先前的光刻機競爭對手早已經陸續退出市場,使得 ASML 把握著全球主要的先進光刻機產能,近年來, IMEC 一直在與 ASML 研究新的 EUV 光刻機,目標是將工藝規模縮小到 1nm 及以下。

目前, ASML 已經完成了 NXE: 5000 系列的高 NAEUV 曝光系統的基本設計,至於設備的商業化。至少要等到 2022 年,而等到台積電和三星拿到設備,要到 2023 年了。

前不久,中國中科院的研究人員宣布,已經突破了設計 2nm 晶片的瓶頸,成功地掌握了設計 2nm 晶片的技術,這樣的發展進程雖然讓人們欣喜,但其實還是存在著比較多的問題。雖然我們已經有了這方面的技術研究突破,但是沒有 EUV 設備的話,是不能夠實現生產的。這從一個側面反應出了 EUV 光刻機的重要性。也正是因為如此,全世界有先進製程能力的晶圓廠都將注意力集中到了 ASML 身上。

材料和工藝

對於像 2nm 這樣先進的製程工藝來說,互連技術的跟進是關鍵。傳統上,一般採用銅互連,但是,發展到 2nm ,相應的電阻電容(RC)延遲問題非常突出,因為,產業正在積極尋找銅的替代方案。目前,朝向 2nm 及更先進製程的新型互連技術主要包括:混合金屬化或預填充,將不同的金屬嵌套工藝與新材料相結合,以實現更小的互連和更少的延遲;半金屬嵌套,使用減法蝕刻,實現微小的互連;超級通孔、石墨烯互連和其他技術。這些都在研發中。

以混合金屬化為例,該工藝在互連中使用兩種不同的金屬。對於 2nm 來說,這很有意義,至少對一層來說是這樣。與雙金屬嵌套相比,通孔電阻更低,可靠性會提高,同時可以保持互連中銅的低電阻率。 ”

業界還一直探索在互連中使用釕材料作為襯墊。釕以改善銅的潤濕性和填充間隙而聞名,雖然釕具有優異的銅潤濕性,但它也有其他缺點,例如電遷移壽命較短,以及化學機械拋光等單元工藝挑戰。這減少了產業中釕襯墊的使用。

其它新的互連解決方案也會陸續出現,但它們可能要到 2023 / 2024 年的 2nm 量產時才會商用。根據 IMEC 的路線圖,產業可以從今天的雙金屬嵌套工藝轉移到下一代技術,稱為 2nm 混合金屬化。接下來將還會有半金屬嵌套和其它方案。

台積電在材料上的研究,也讓 2nm 及更先進製程量產成為可能。據悉,台積電和台灣交大聯手,開發出全球最薄、厚度只有 0.7 奈米的超薄二維半導體材料絕緣體,可望藉此進一步開發出 2nm ,甚至是 1nm 的電晶體通道。

EDA 工具

新的製程工藝離不開 EDA 工具的支持, 2nm 也不例外,業內兩大 EDA 廠商也早有相應的布局。面對如此高精尖的製程工藝,Cadence 和 Synopsys 創建了全新的 EDA 工具堆棧,並開發全新的IP庫。 2nm 製程要求晶片開發人員必須採用全新的設計規則和流程,並重新製作他們以前可能使用過的所有內容。就像在 2014 年至 2015 年轉向 FinFET 結構一樣,增加晶片設計成本的同時,採用 GAA FET可能會再次增加設計成本。

Synopsys 表示,Liberty技術顧問委員會(LTAB)和互連建模技術顧問委員會(IMTAB)批准了新的建模結構,用以解決工藝節點低至 2nm 的時序和寄生參數提取問題。行動設備對超低功耗的要求以及各種製造挑戰,需要新的方法來確保在signoff時達到最佳精度,同時支持設計工具針對最低功耗進行優化。此外,這些節點上的器件架構、掩模和成像技術促使工件必須通過互連工藝文件(ITF)中的新擴展來建模。

Synopsys 還推出了 DTCO 設計方法學,用以整合各種先進工藝。據悉, DTCO 已經幫助客戶實現 2nm 工藝設計。

客戶

不久前,台積電總裁魏哲家表示,台積電製程每前進一個世代,客戶的產品速度效能提升 30% ~ 40% ,功耗可以降低 20% ~ 30% 。這或許是該公司不斷追求先進製程的關鍵所在。

目前來看,台積電將在業內率先量產 2nm 製程晶片已無懸念。而作為其近些年的頭號客戶,蘋果(Apple, AAPL-US)成為最先嚐鮮 2nm 晶片的廠商,也在情理之中。此外, 2024 年之後,高通(Qualcomm, QCOM-US)、輝達(NVIDIA, NVDA-US)、AMD(Advanced Micro Devices, AMD-US)等都會成為其 2nm 技術的客戶。

目前,以台積電的 2nm 研發進度來看, 2024 年正式量產沒有問題。也有報導指出,台積電已經在研究 2024 年的 2nm iPhone處理器,並且已經開始研究 1nm 製程節點技術。

《虎嗅網》授權轉載

【延伸閱讀】

全球CMOS影像感測器的領導廠商.png)