MOSFET,簡稱「MOS」,其全稱為金屬—氧化物—半導體場效電晶體(MOSFET:Metal Oxide Semiconductor Field Effect Transistor)。無論在 IC 設計裡,還是電路板應用上,都十分廣泛。尤其在大功率半導體領域,各種結構的 MOSFET 更是發揮著不可替代的作用。

許多電子產品的零件組成,需要「MOSFET」,因此也會與 MOSFET 相關個股有密切相關!例如:電腦、平板電腦、智慧型手機及相關工業用品… 等。不過 MOSFET 是什麼?究竟長什麼樣子?

MOSFET 是什麼?

MOSFET 是功率離散元件的主體之一,扮演著電源電子控制的角色(可以想像成是開關)。依照不同的導電特性與通道的差異,又可分為 NMOS、PMOS、CMOS 三種:

NMOS(N-type MOS)

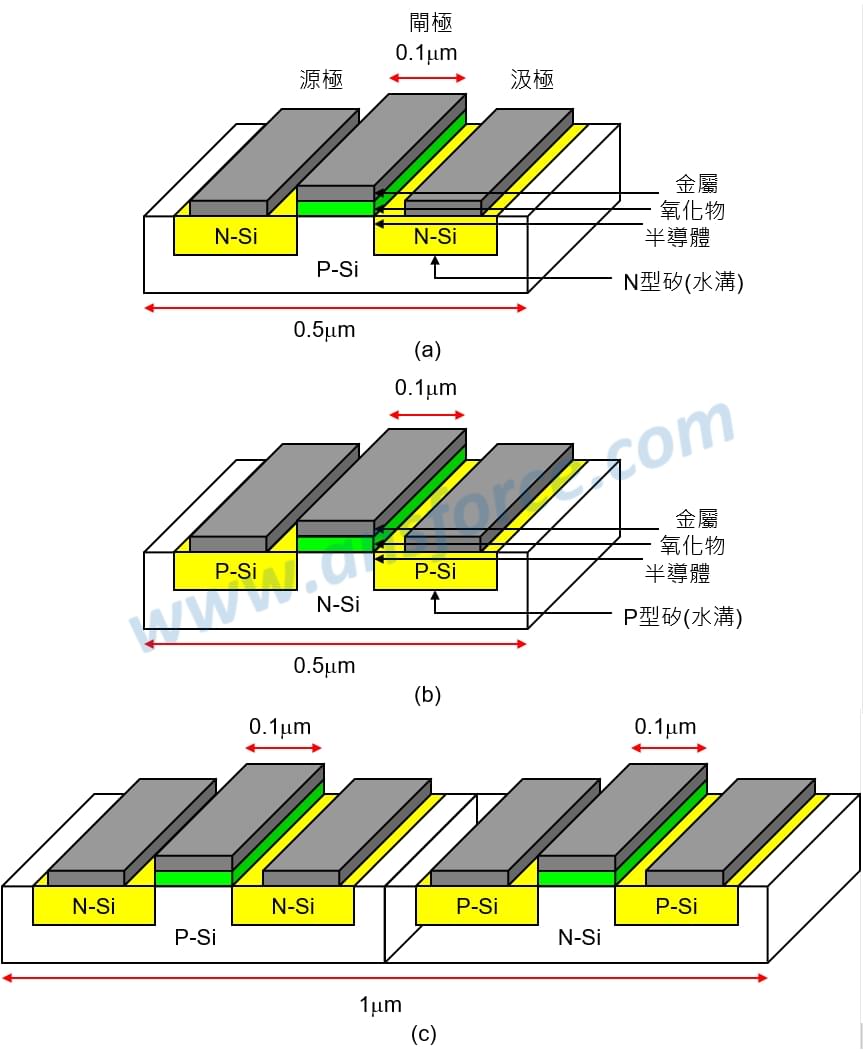

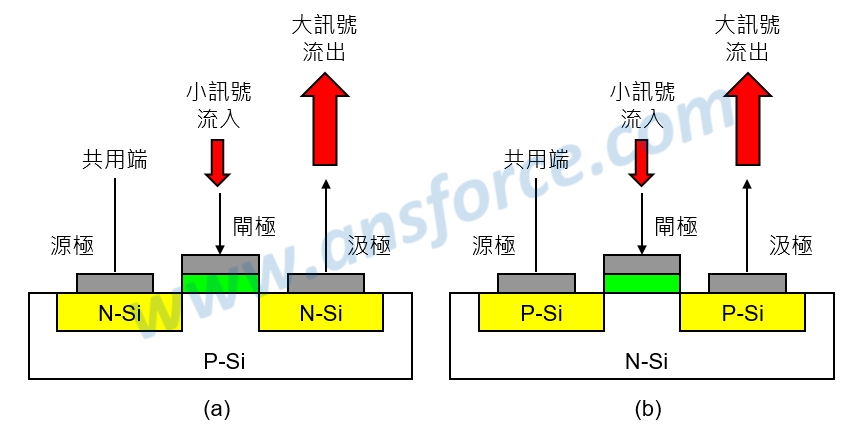

NMOS 的構造如 <圖一 (a)> 所示,在 P 型矽基板的左右各製作一個 N 型的區域(類似「水溝」的構造),並且在上方蒸鍍金屬電極;另外在矽基板的中央上方製作一層氧化矽,上方再蒸鍍一層金屬電極(目前大多使用多晶矽取代),中央的金屬稱為「閘極(Gate)」,左邊的金屬稱為「源極(Source)」,右邊的金屬稱為「汲極(Drain)」。

PMOS(P-type MOS)

PMOS 的構造如 <圖一 (b)> 所示,與 NMOS 相同,但是 N 型與 P 型區域相反,因此導電特性相反。

CMOS(Complementary MOS)

CMOS 的構造如 <圖一 (c)> 所示,由「一個 NMOS」+「一個 PMOS」組合起來形成一個 CMOS,是目前最常使用的一種主動元件。

圖一、MOS 與 CMOS 的構造

閘極長度(Gate length)

由 <圖一> 可以看出,MOS 的閘極長度大約 0.1μm(微米),所以 NMOS 與 PMOS 的尺寸大約 0.5 μm,MOS 的尺寸大約 1 μm。

閘極長度是所有構造中最細小也最難製作的,因此我們常常以閘極長度來代表半導體製程的進步程度,這就是所謂的「製程線寬」。閘極長度會隨製程技術的進步而變小,從早期的 0.18 微米、0.13 微米,進步到 90 奈米、65 奈米、45 奈米、22 奈米,到目前最新製程 10 奈米。當閘極長度愈小,則整個 MOS 就愈小,而同樣含有數十億個 MOS 的晶片就愈小,封裝以後的積體電路就愈小,最後做出來的手機就愈小囉!

【備註】製程線寬其實就是閘極長度,只是圖一看起來 10 奈米的閘極長度反而比較短,因此有人習慣把它叫做「線寬」。

MOSFET 應用

MOS 開關(MOS switch)

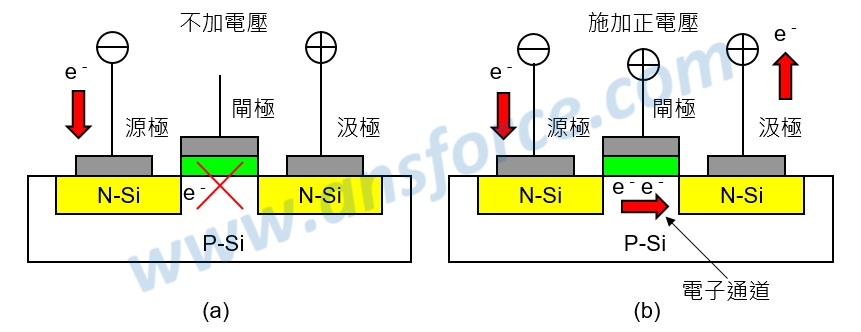

NMOS 開關的工作原理如 <圖三> 所示,將電子由左邊的源極(N 型水溝)注入,經過中央的閘極下方(P 型通道)以後,再由右邊的汲極(N 型水溝)流出,是否要讓電子通過,則由閘極「不加電壓(關)」或「施加電壓(開)」來控制:

閘極不加電壓

- 電子由左邊的源極(N 型水溝)注入以後,由於閘極下方為 P 型不導電子,故電子無法通過,形成斷路,代表 0,如 <圖二 (a)> 所示。

閘極施加電壓

- 電子由左邊的源極(N 型水溝)注入以後,由於閘極施加正電壓吸引下方 P 型矽晶圓中的少量電子浮到表面,形成含有電子的通道(Channel),電子沿著通道繼續前進,形成通路,代表 1,如 <圖二 (b)> 所示。

我們就是利用閘極快速地「不加電壓(關)」或「施加電壓(開)」,來控制電子的「不導通」或「導通」,進行 0 與 1 的快速運算。

圖二、NMOS開關的工作原理

一個積體電路(IC)含有許多的 MOS,就可以進行一大堆 0 與 1 的運算,這就是個人電腦與「數位積體電路」工作的基本原理,除了 NMOS 以外,PMOS 或 CMOS 都可以做為開關來使用,在此不再詳細討論。

MOS 放大器(MOS amplifier)

使用 NMOS 除了可以當開關,也可以做為放大器,其工作原理如 <圖三 (a)> 所示,將「較小的電壓或電流(小訊號)」輸入閘極(Gate),由於 NMOS 的元件特性會使訊號放大,轉變成「較大的電壓或電流(大訊號)」由汲極(Drain)輸出,這就是「類比積體電路」工作的基本原理,除了 NMOS 以外,PMOS 或 CMOS 都可以做為放大器來使用,其工作原理如 <圖三 (b)> 所示,在此不再詳細討論。

圖三、NMOS 放大器的工作原理

CMOS 開關與放大器

由上面的描述可以得知,MOS 說穿了就是一種「開關」,也就是可以控制 0 與 1 的元件,我們利用這種元件來製作可以處理數位訊號(0 與 1)的積體電路(IC),但是目前市面上幾乎所有的積體電路(IC)都是使用 CMOS 來製作,而不是使用 NMOS 或 PMOS。

由 <圖一> 能看出 CMOS 是由一個 NMOS 與一個 PMOS 組合而成,雖然功能與單獨一個 NMOS 相同,但是 CMOS 的體積是單獨一個 NMOS 的二倍,製作成本較高,為什麼積體電路(IC)會使用成本較高的 CMOS 來製作呢?

因為 CMOS 只有在處理數位訊號由 0 變 1 或由 1 變 0 時才會消秏電能(動態功率耗損),如果一直保持 0 或一直保持 1 時並不會消秏電能(靜態功率耗損),因此比單獨一個 NMOS 或 PMOS 還要省電,符合目前所有電子產品省電的要求,所以目前幾乎所有的積體電路(IC)實際上都是使用 CMOS 來製作,換句話說,目前的積體電路是:犧牲大小,成全省電。

《知識力》授權轉載

【延伸閱讀】

全球CMOS影像感測器的領導廠商.png)

商品期貨基本面分析:供需平衡表_-.png)