從 1960 年代到 2010 年代,縮小電晶體的工程創新大約每兩年使單個電腦晶片的電晶體數量增加一倍,摩爾定律引領了晶片速度和效率的持續提高。

10nm 、 7nm 、 5nm 、 3nm,這些逐漸縮小的晶片製程數字,正是全球電子產品整體性能不斷進化的核心驅動力。隨著製造更小的電晶體工程難度逐漸加劇,甚至無法解決,從而導致半導體產業的資本支出和人才成本以不可持續的速度成長。

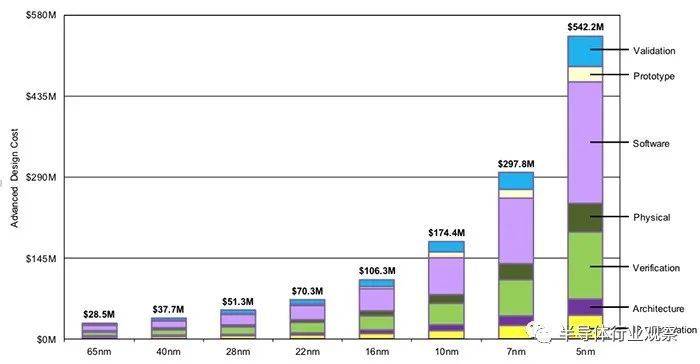

在先進工藝設計成本上,知名半導體技術研究機構 Semiengingeering 也統計了不同工藝下晶片所需費用,其中 28nm 節點上開發晶片只要 5,130 萬美元投入, 16nm 節點需要 1 億美元, 7nm 節點需要 2.97 億美元,到了 5nm 節點,開發晶片的費用將達到 5.42 億美元, 3nm 節點的數據還沒有,大概是因為 3nm 現在還在研發階段,成本不好估算。但從這個趨勢來看, 3nm 晶片研發費用或將接近 10 億美元。

▲先進工藝設計成本(圖源:Semiengingeering)

按照台積電( 2330-TW )、三星( 5007-TW )的說法,可見,先進晶片的燒錢遊戲正在加速。IBS 數據顯示, 3nm 工藝開發將耗資 40 億至 50 億美元,而興建一條 3nm 產線的成本約為 150 億~ 200 億美元。這一數據也解釋了為什麼台積電先前宣布的 3nm 晶圓廠需要 200 億美元投資的原因。而三星為了進入 3nm 工藝,投的錢一點都不比台積電少,單從這一點來看,很多晶片製造企業就沒有這個實力。

的確,製程工藝的研發和生產成本逐代上漲,飆高的技術難度和研發成本將大多數晶片代工廠攔在半山腰。 2018 年,因高昂的研發成本,當時排名世界第二的代工廠格羅方德被迫放棄 7nm 製程的研發。在全球備戰 3nm 及更先進製程工藝節點之際,本文圍繞晶片設計和製造中的多個關鍵節點,來分析一下 3nm 晶片或先進製程晶片的成本究竟為何達到如此之高。

先進製程晶片成本為什麼這麼貴?

根據晶片的製造流程,可以分為主產業鏈和支撐產業鏈:主產業鏈包括晶片設計、製造和封測;支撐產業鏈包括 IP 、 EDA 、裝備和材料等。其中,同時晶片製造環節涉及到的晶圓廠投資、晶圓製造以及相關設備成本也將會分攤到晶片整體成本之中。工藝製程越先進,成本更是隨之提高。

晶圓代工成本

根據 CEST 的模型,在 5nm 節點上構建的單個 300mm 晶圓的成本約為 16,988 美元,在 7nm 節點上構建的類似晶圓成本為 9,346 美元。可以看到,相同尺寸晶圓, 5nm 工藝節點相比 7nm 每片晶圓代工售價高 7,000 多美元。

▲按節點計算 2020 年每個晶片的代工銷售價格(圖源:CSET)

從中可以推斷出,在 3nm 節點上構建的晶圓成本或將達到 3 萬美元左右,晶圓代工成本將進一步提高。

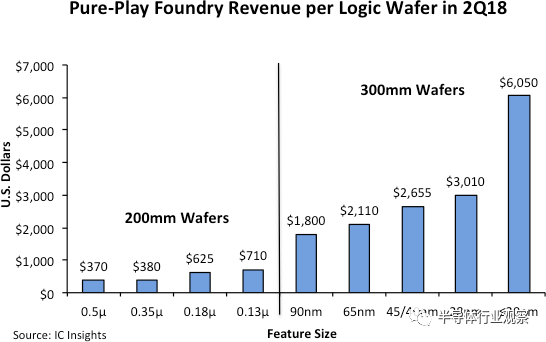

另一組數據也對此進行了印證,IC Insights 提供的數據顯示,每片 0.5 µ 200mm 晶圓代工收入 即使同樣是在 300mm 晶圓尺寸下,≤ 20nm 相比 28nm 工藝,成本相差也達到一倍。

▲2018 年主要技術節點和晶圓尺寸的每片晶圓代工收入(圖源:IC Insights)

此外,除了晶圓廠建設和代工費用,晶圓製造廠商的日常營運投入也不低。台積電企業社會責任報告書中的數據顯示, 2019 年台積電全球能源消耗量達到 143.3 億度,作為對比, 2019 年深圳市 1,343.88 萬常住人口的全年居民用電為 146.64 億度。由此可見,台積電一年消耗的電量有多麼巨大。

而且,精度越高的工藝,或精度越高的光刻設備,所需電量還會成正比成長。根據報導,以 5nm 為例,台積電 5nm 晶片大規模量產之際,公司單位產品用電量相比 2019 年上漲了 17.9% 。

光罩(Mask)成本

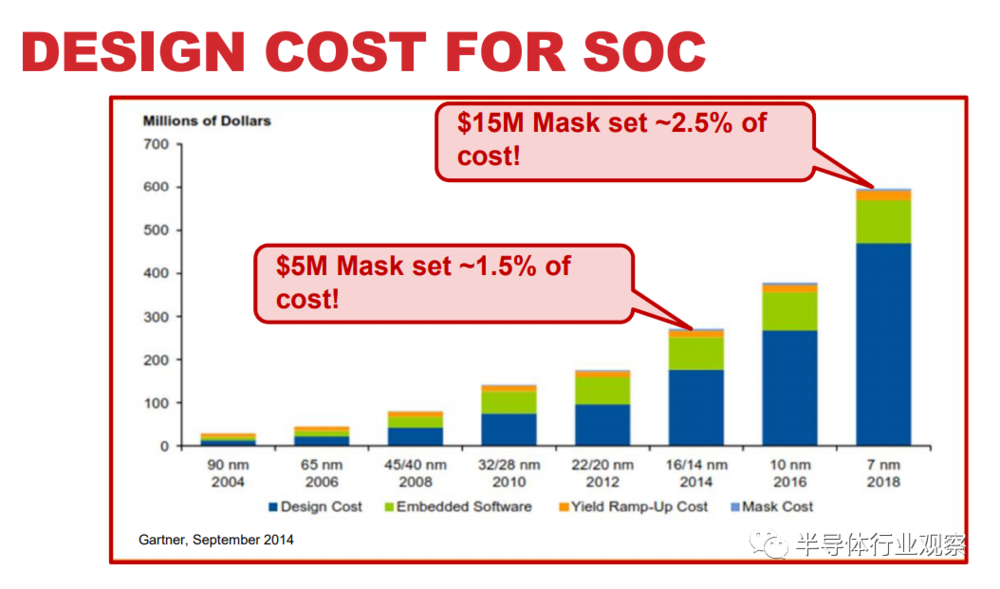

光罩版又稱光罩、掩膜等,是微電子製造過程中的圖形轉移工具或母版,其功能類似於傳統照相機的 “ 底片 ” ,根據客戶所需要的圖形,通過光刻製版工藝,將微米級和奈米級的精細圖案刻製於光罩版基板上,是承載圖形設計和工藝技術等內容的載體。據 IBS 數據顯示,在 16/14 nm 製程中,所用光罩成本在 500 萬美元左右,到 7nm 製程時,光罩成本迅速升至 1,500 萬美元。

▲7nm 製程中,光罩成本大概為 1500 萬美元(圖源:IBS)

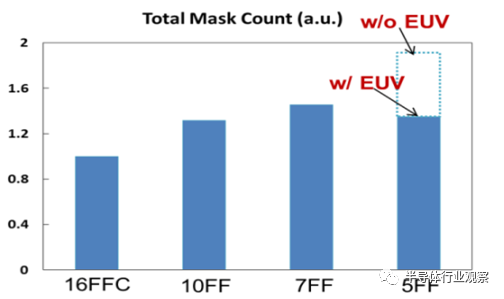

▲不同製程中的 Mask 數量(圖源:台積電)

但是,在光罩數量基本持平的情況下,更先進的製程工藝使得光罩總成本提升,能側面反映出光罩平均成本在不斷升高。

再反映到晶片成本上,每片 CPU 的光罩成本等於光罩總成本/總產量。如果總體產量小,晶片的成本會因為光罩成本而較高;如果產量足夠大,比如每年出貨以億計,光罩成本被巨大的產量分攤,可以使每塊 CPU 的光罩成本大幅降低,使擁有 “ 更貴的製程工藝 + 更大的產量 ” 屬性的 CPU,比 “ 便宜的製程工藝 + 較小的產量 ” 的 CPU 成本更低。

可以預見,到 3nm 時,光罩成本預計將會再度攀升,進一步增加晶片成本。

EUV 光刻機

光刻機作為晶片製造階段最核心的設備之一,負責 “ 雕刻 ” 電路圖案,其精度決定了製程的精度,其原理是把設計好的晶片圖案印在光罩上,接著用激光光束穿過印著圖案的光罩和光學鏡片,將晶片圖案曝光在帶有光刻膠塗層的矽晶片,最終將光罩上的圖案轉移到晶片光刻膠塗層上。

隨著工藝製程的發展,到 7nm 及更先進的技術節點時,需要波長更短的極紫外線,而荷蘭 ASML 是全球唯一有能力製造 EUV 光刻機的廠商。

台積電在 7nm + 時引入了 EUV 設備,但層數相對有限; 6nm 增加了 EUV 層並優化了 PDK 隨著晶片面向 3nm 及更先進的工藝,晶片製造商將需要一種高數值孔徑 EUV 據 ASML 財報顯示,他們正在研發採用 high-NA 技術的下一代 EUV 光刻機,有更高的數值孔徑、解析度和覆蓋能力,較目前的 EUV 光刻機將提高 70% 。

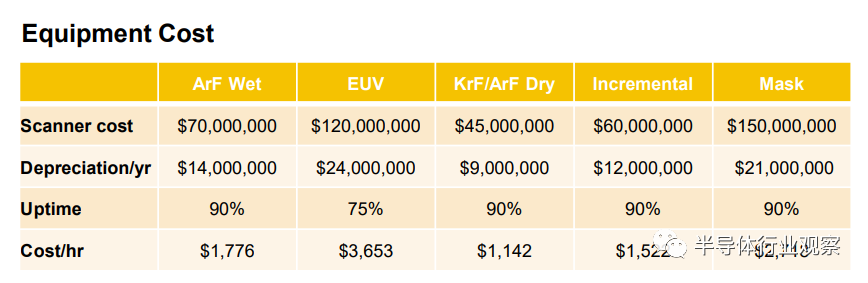

但 EUV 光刻機的價格一直以來十分昂貴, 2018 年,中芯國際( 00981-HK )和 ASML 簽訂了訂購協議,以 1.2 億美元的價格訂購了一台 EUV 光刻機。這一價格與 PHOTRONICS 揭露的 EUV 光刻機價格基本吻合。

▲設備成本(圖源:PHOTRONICS)

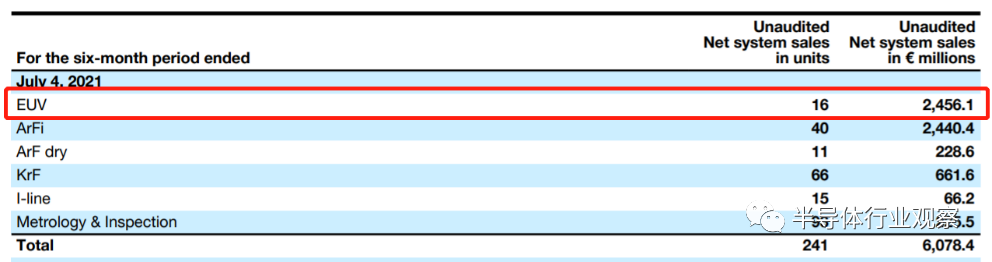

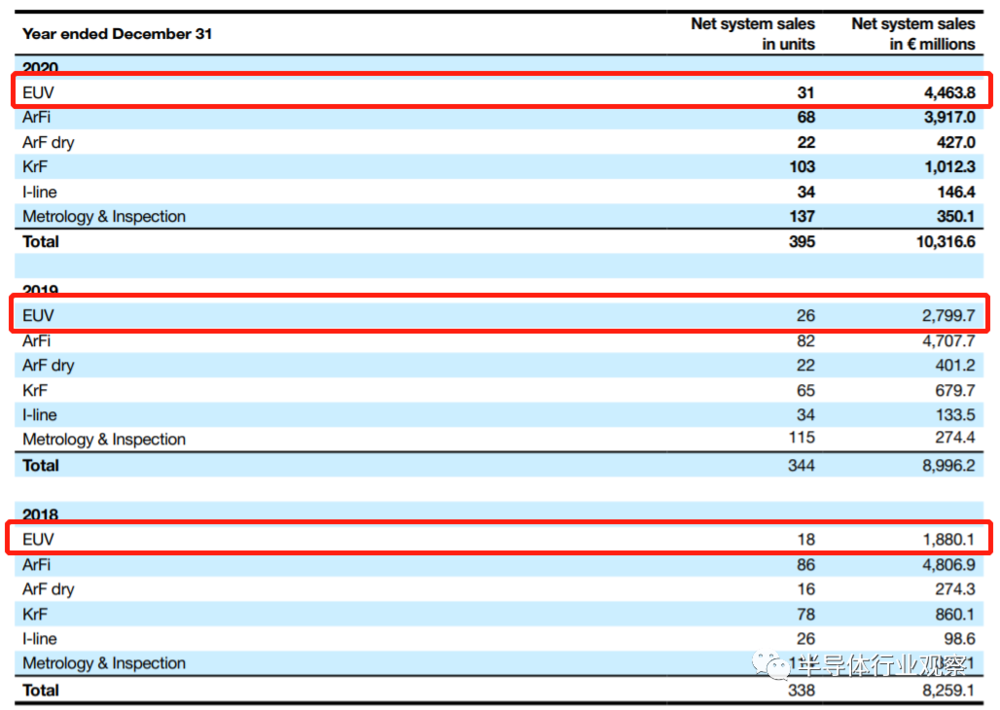

從 ASML 最新公布的 2021 年第二季度財報來看,截止 2021 年 7 月 4 日,ASML 今年出貨 EUV 光刻機 16 台,銷售額達到 24.561 億歐元,平均每台 EUV 光刻機價格高達 1.535 億歐元。

▲ASML 2021 年 Q2 財報(圖源:ASML)

▲ASML 近三年財報(圖源:ASML)

一台 EUV 光刻機售價超過 1 億美元,而且還相當不好買。ASML 每推出一代 EUV 光刻機,新設備的生產能力在穩步提升,但價格自然更高。據揭露,ASML 第二代 EUV 光刻機將會是 NXE: 5000 系列,進一步提高光刻精度,原計劃 2023 年問世,現延遲到 2025 ~ 2026 年,而價格預計將突破 3 億美元。

當然,除了價格最貴的 EUV 光刻機之外,沉積、刻蝕、清洗、封裝等環節所採用的設備和材料也價格不菲,且成本都在隨著工藝製程向前發展不斷提高。

研發與人力成本

先進製程不僅需要巨額的建設成本,高昂的研發和人力費用也提高了設計企業的門檻。

晶片設計包含電路設計、版圖設計和光罩製作等,需要考慮多方面因素和知識結構。以大家較為熟悉的 5G SoC 為例,產業廠商能夠集成自研的獨立 AI 處理單元 APU,多模通訊基頻、相機 ISP、各種控制開關、微核等多個自研模組。這部分成本很難具體估算,屬於長期的研發成果,但投入力度從人力成本中可見一斑。

人力成本是研發成本的重要部分,項目開發效率和質量與工程師數量和水平相關,國內資深晶片設計工程師年薪一般在 50-100 萬元之間。據了解,賽靈思在研發代號 Everest 的 7nm 工藝的 FPGA 晶片時提到,費時 4 年,動用了 1,500 名工程師才開發成功,項目耗資超過 10 億美元。FPGA 晶片已經如此,更複雜的高端 CPU、GPU 晶片所需要的投資更是巨額數字,輝達(NVIDIA, NVDA-US)開發 Xavier 動用了 2,000 個工程師,開發費用已達 20 億美金。

晶片的開發成本取決於晶片尺寸、晶片類型等。綜合來看,隨著晶片設計種類和形態千差萬別,且正在不斷發生變化,難以預測其具體成本。

另一方面,電晶體架構轉向 GAA,也在增加晶片成本。目前隨著深寬比不斷拉高,FinFET 逼近物理極限,為了製造出密度更高的晶片,環繞式柵極電晶體,電晶體結構從 FinFET 走向 GAA,成為摩爾定律續命的關鍵。

三星、台積電、英特爾(Intel, INTC-US)均引入 GAA 技術的研究,其中三星已經先一步將 GAA 用於 3nm 晶片設計。然而 GAA 當下還面臨包括 n/p 不平衡、底部板的有效性、內部間隔、柵極長度控制和器件覆蓋等在內的各種挑戰。在科技變革的過程中,新的技術需要更多時間來開發,在各環節需要新的技術和設備,這一切都在加大晶片開發的成本。

EDA 成本

EDA 涵蓋了積體電路設計、驗證和仿真等所有流程,晶片的用途、規格、特性、製成工藝幾乎全都在這個階段完成。利用 EDA 工具可設計得到極其複雜的電路圖,從而製造出功能強大的晶片。

根據 ESD Alliance 數據顯示, 2020 年 EDA 全球市場規模 114.67 億美元,相對於幾千億美元的晶片市場來說佔比較小,但 EDA 對晶片設計的效率和成本都起著至關重要的作用。

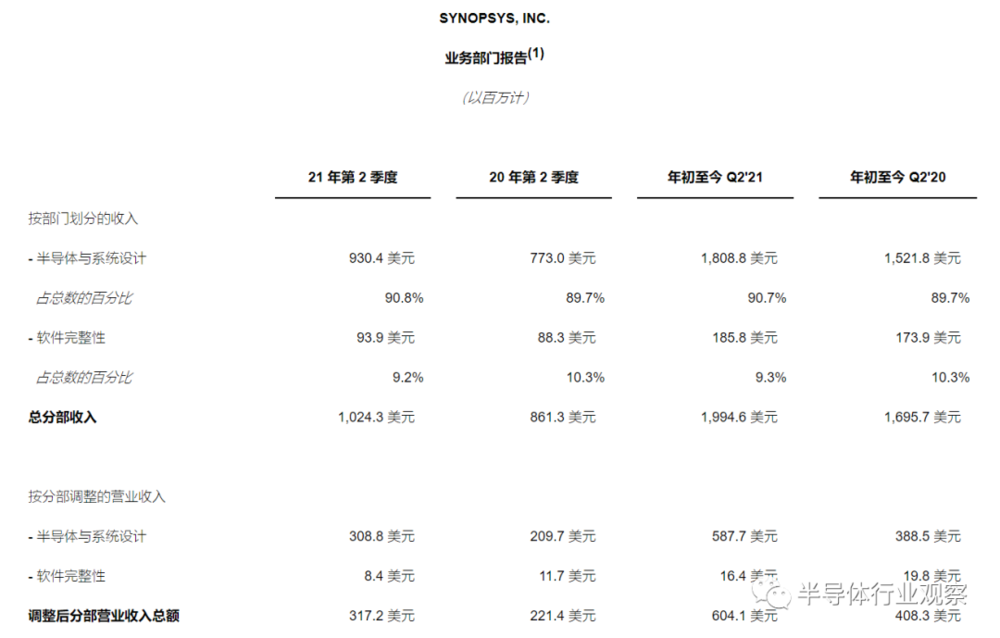

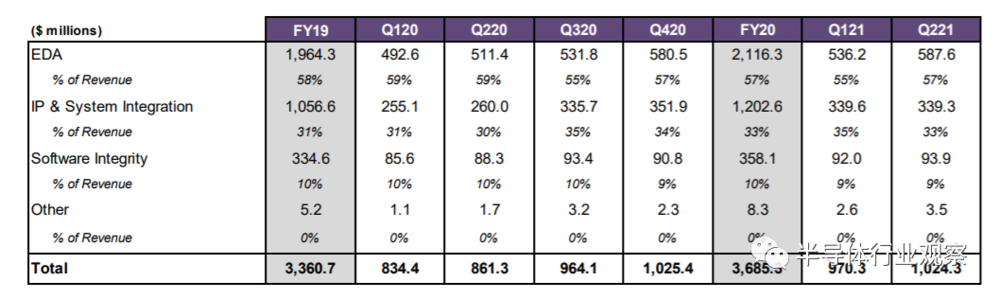

EDA 是一個市場規模雖然小但技術流程很長的產業,需要種類繁多的軟硬體工具相互配合從而形成工具鏈,以 EDA 巨頭 Synopsys為例,其完整覆蓋晶片全設計流程的工具鏈號稱有 500 多種。從 Synopsys 和 Cadence 的財報來看, 2020 年營收分別為 36.9 、 26.8 億美元,兩家公司每年花費在研發上的投入達到 35% 以上,Synopsys 的研發費用更是達到驚人的十億美金級別, EDA 軟體的研發成本正在加速提升。

▲Synopsys 2021 年 Q2 財報(圖源:Synopsys)

根據 Synopsys 最新財報來數據, 2021 年第二季度營收 10.243 億美元,半導體和系統設計,包括 EDA 工具、 IP 產品、系統集成解決方案和相關服務;軟體完整性,包括用於軟體開發的安全和質量解決方案等。 EDA 營收達到 5.876 億美元,佔比在 57% 左右。

▲Synopsys 財報數據(圖源:Synopsys)

據網路上數據, 20 人的研發團隊設計一款晶片所需要的 EDA 工具採購費用在 100 萬美元/年。從 EDA 的產業屬性及高昂的研發投入能夠預測,待到 3nm 製程時, EDA 工具授權費自然更是不菲。

IP 授權成本

半導體 IP 是指在積體電路設計中那些已驗證、可複用、具有某種確定功能和自主智慧財產權功能的設計模組,晶片公司可以通過購買 IP 實現某個特定功能。

晶片設計主要由於晶片核心的底層架構 據了解,ARM 在過去通常要求客戶選擇一種特定的晶片設計方案,並預先為其支付授權許可費,這種模式一般都需要廠商一次性花費數百萬美元才能被允許使用。

另一方面,根據 Synopsys 和 Cadence 業績數據,Synopsys 公司 IP 和系統集成部份營收佔比從 2017 年的 28% 提升至 2020 年的 33% ,達到 1202.6 萬美元;Cadence公司 IP 部分佔比從 2016 年的 11% 提升至 2020 年的 14% 。

▲2017-2020 年 Synopsys 營收拆分(單位:百萬美元)

可見 IP 作為技術含量最高的價值節點,隨著晶片製程越來越先進,晶片價格的提升, IP 研發難度和授權費用也將隨之升高。

結論

上述種種因素和環節疊加之下,先進製程的晶片成本自然是居高不下。

筆者做不到對 3nm 或任何工藝節點的成本價格進行精確推算和預測,只是在能夠蒐集到有限的數據基礎上得出盡可能客觀的觀點。同時希望大家能夠基於此,更好的理解先進工藝對晶片成本帶來巨大提升的原因所在。目前,隨著半導體製程的不斷發展,摩爾定律的推進節奏逐漸趨緩,晶片成本問題成為阻礙先進製程發展的重要因素,但成本又絕不會是其根本原因。說到底,錢終歸只是輔助作用。

FinFET 技術發明人胡正明教授曾說過,半導體產業大約每隔 20 年就會有新的危機出現。 20 年前,大家一度非常悲觀,看不清如何才能將晶片性能做得更好、功耗更低且控制住成本。如今,半導體產業或是又來到了 20 年週期的危機循環節點,延續摩爾定律的生命力需要的是創新技術和設備的突破。當先進製程走到 3nm 、 2nm 、 1nm 後,未來半導體產業的發展,路又在何方?

《虎嗅網》授權轉載

【延伸閱讀】