系統單封裝(SiP:System in a Package)

將數個功能不同的晶片(Chip),直接封裝成具有完整功能的「一個」積體電路(IC),稱為「系統單封裝(SiP:System in a Package)」。

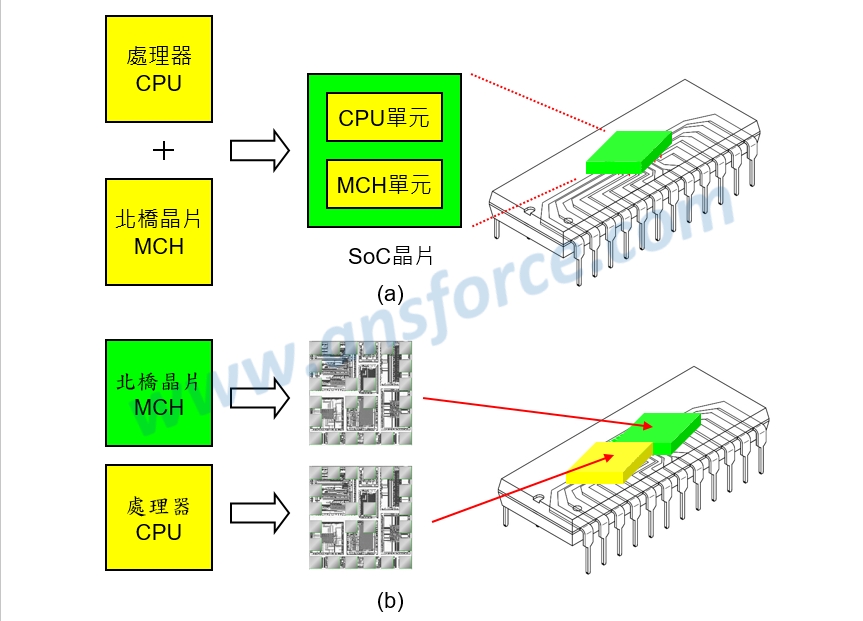

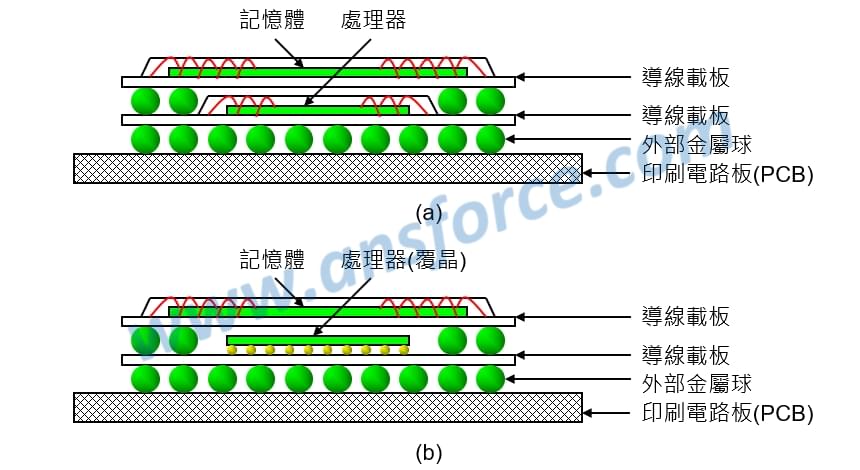

前面曾經提過,要將不同功能的積體電路(IC)整合成一個 SoC 晶片,稱為「系統單晶片(SoC:System on a Chip)」,如<圖一(a)>所示,有許多困難需要克服,那就改變方法,直接將它們封裝成一個積體電路(IC)。例如:將個人電腦的處理器(CPU)與北橋晶片(MCH)封裝成一個積體電路(IC),如<圖一(b)>所示,

此時仍然是兩個獨立的晶片,只是封裝在同一個外殼而已,困難度大為降低,在某些特別的應用上,甚至可以將被動元件、連接器、天線等一起封裝進去。

圖一、系統單晶片(SoC)與系統單封裝(SiP)示意圖

系統單封裝的優點

➤減少體積:將不同功能的晶片與被動元件封裝成一個積體電路(IC),體積較小(但是仍然比 SoC 晶片體積大一些)

➤比 SoC 晶片容易整合: SoC 晶片不同「功能單元」之間的製程技術不同,要製作在一塊矽晶晶片非常困難;系統單封裝(SiP)只是將不同功能的晶片與被動元件封裝成一個積體電路(IC),容易許多。

➤降低印刷電路板線路複雜度:將不同功能的晶片與被動元件封裝成一個積體電路(IC),可以減少印刷電路板上的積體電路(IC),降低線路的複雜度。

➤提升系統功能:將不同功能的晶片與被動元件封裝成一個積體電路(IC),可以整合更多不同功能的元件,提升系統的功能。

➤加快產品上市時間:系統單封裝(SiP)製程較系統單晶片(SoC)容易,可以加快產品上市的時間。

系統單封裝的挑戰

一般而言,系統單封裝(SiP)並不是隨便將兩個晶片封裝在一起就可以,而是必須滿足下列條件才行:

➤封裝後體積必須變小:將不同功能的晶片與被動元件封裝成一個積體電路(IC),所以封裝後體積必定比個別數個積體電路(IC)還小。

➤必須整合各種類型的封裝技術:必須將數種不同類型的封裝技術整合在一起,與單純將多個晶片封裝在一起的小型封裝技術不同。

➤必須包含各種類型的主動與被動元件:必須包含處理器、記憶體、邏輯元件、類比元件等數個晶片,甚至必須將被動元件、連接器、天線等一起封裝進去。

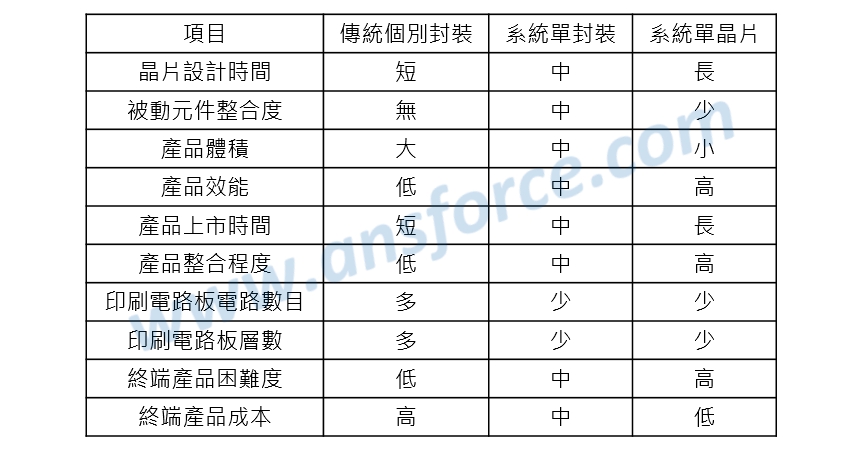

傳統個別封裝技術、系統單晶片(SoC)、系統單封裝(SiP)的比較如<表一>所示,基本上系統單晶片(SoC)具有較多的優點,但是技術困難度較高,因此遇到無法整合成單一 SoC 晶片的時候,常常使用系統單封裝(SiP)來取代。

表一、傳統個別封裝技術、系統單晶片(SoC)、系統單封裝(SiP)比較表

系統單封裝(SiP)的種類

系統單封裝(SiP)的技術經過十年來的發展,慢慢成為縮小積體電路(IC)體積的一個方法,目前主要有下列幾種常見的系統單封裝(SiP):

➤PiP(Package in Package)封裝:系統單封裝(SiP)可以左右堆疊,如<圖二(a)>所示,也可以上下堆疊,如<圖二(b)>所示,另外一種類似的封裝方式稱為「PiP(Package in Package)封裝」,就是把兩個封裝好的積體電路再堆疊起來,如<圖二(c)>所示。

由於手機需要很小的體積,目前都是把處理器與記憶體兩個晶片封裝成一個積體電路(IC)來縮小體積,但是通常生產處理器的廠商並不生產記憶體(韓國三星公司例外)。

圖二、PiP(Package in Package)封裝示意圖

因此,處理器廠商必須向記憶體廠商購買記憶體晶片,再與自己生產的處理器晶片封裝成一個積體電路(IC)才能出貨,如果良率不夠高,封裝時不小心弄壞了記憶體只能報廢,再將報廢的費用轉嫁到產品上,所以售價很難有競爭力。

➤PoP(Package on Package)封裝:將記憶體封裝成一個積體電路(IC),但是這個封裝外殼比較特別,在下方可以連接金屬球,上方的四周圍也可以,而處理器封裝成另外一個積體電路(IC),在下方的四周圍可以連接金屬球,所以處理器可以疊在記憶體上面。

如<圖三(a)>所示,我們稱為「PoP(Package on Package)封裝」,當然上方的處理器或下方的記憶體可以使用「打線封裝」或「覆晶封裝」,如<圖三(b)>所示。

使用這種方法,生產處理器的廠商就不需要再向記憶體廠商購買記憶體晶片,而是由生產手機的廠商自己想辦法解決處理器與記憶體兩個積體電路(IC)疊起來的良率問題,對生產處理器的廠商而言比較方便,售價也比較有競爭力。

圖三、PoP(Package on Package)封裝示意圖,資料來源:www.smtonline.com。

【請注意】上述內容經過適當簡化以適合大眾閱讀,與產業現狀可能會有差異,若您是這個領域的專家想要提供意見,請自行聯絡作者;若有產業與技術問題請參與社群討論。

《知識力》授權轉載

【延伸閱讀】

全球CMOS影像感測器的領導廠商.png)